NOT Gate에 이어 이번에는 NAND Gate를 MobaXterm을 통해 구현해보려 한다.

먼저 개념정리를 하자면, AND일 경우에는 nMOS는 직렬, pMOS는 병렬이고

OR일 경우에는 nMOS는 병렬, pMOS는 직렬로 구성된다.

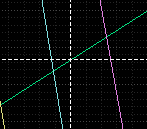

만약 식이 F = (A * B + C)'인 경우에는 다음과 같이 회로가 그려진다.

그런데, 밑에 그림처럼도 그려질 수도 있다.

왼쪽 오른쪽 모두 다 동일한 구조지만, F선을 기준으로 맞닿는 TR의 개수가 다르기 때문에, 왼쪽의 회로도가 더 성능면으로 좋다고 판단할 수 있다. 즉, 딜레이 측면으로 성능이 유리하다.

이번에는 F = (A*B + C*D)'의 회로를 그려보자.

다음과 같이 회로가 그려진다.

2 NAND

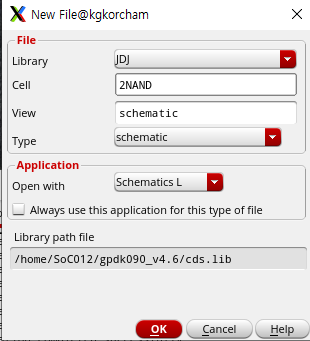

2 NAND를 설계하기 위해 다음과 같이 새로운 Cell View를 만든다.

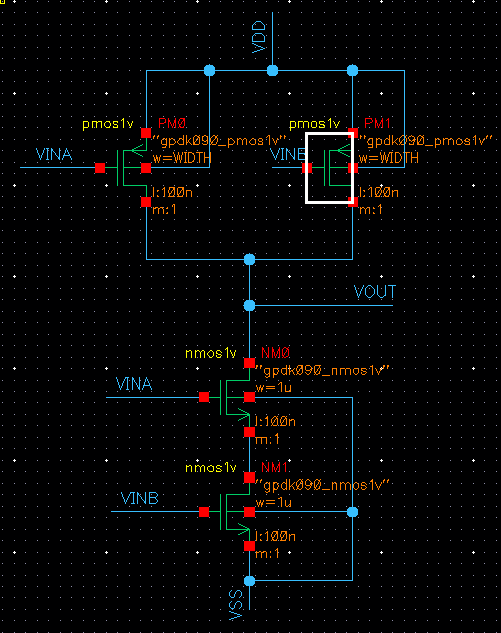

다음과 같이 회로를 구성하였다.

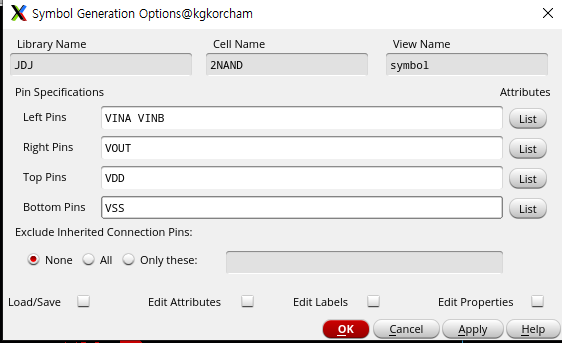

심벌화를 하기 위해 다음과 같이 설정한다.

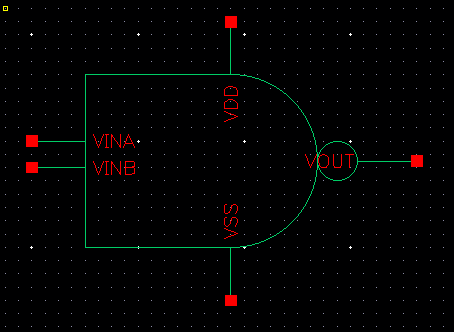

그러고 나서 다음과 같이 NAND Gate 모양을 만들어 준다.

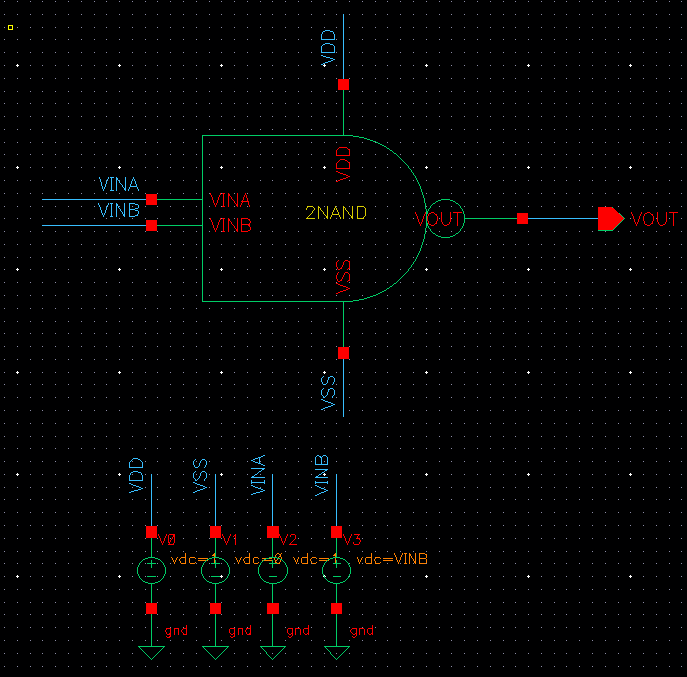

이제 만들어진 NAND를 test 하기 위해 새로운 창을 만들어 다음과 같이 핀과 라벨을 부여한다.

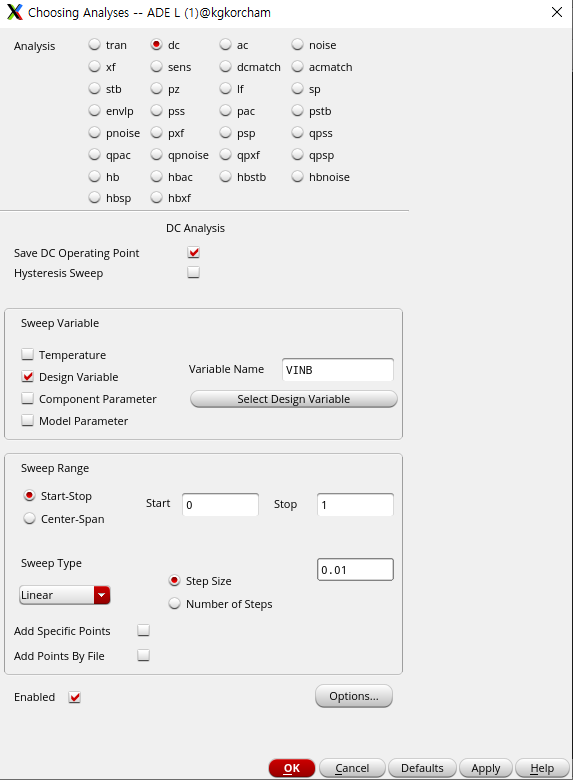

다음과 같이 측정 범위를 기입한다.

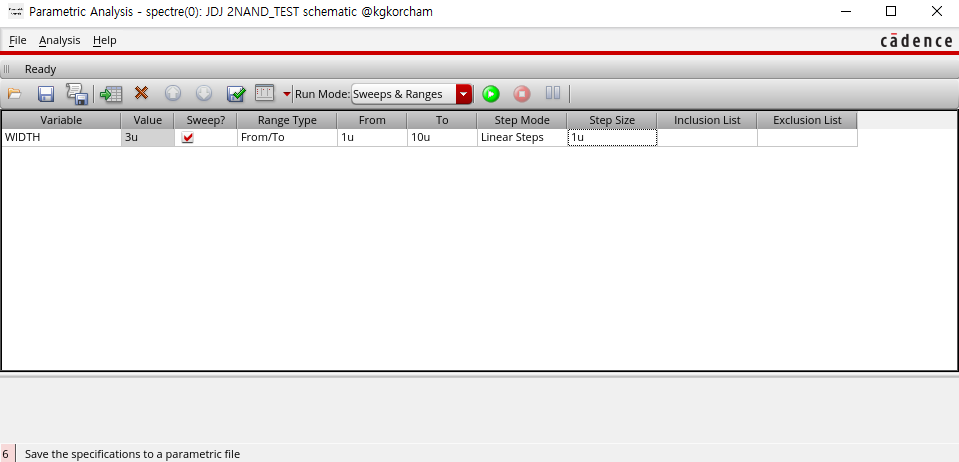

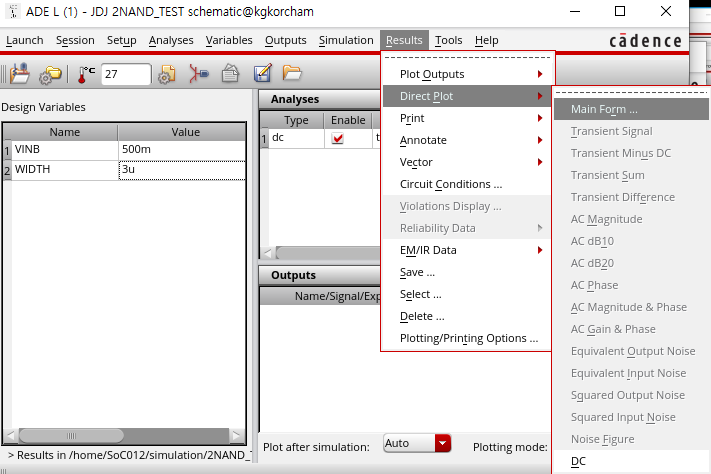

아래 창과 같이 설정한 후 초록색 실행창을 누르고 100퍼센트가 되면 다음 과정으로 넘어간다.

ADE L창에서 Results에서 Main Form을 통해 그래프를 확인해 본다.

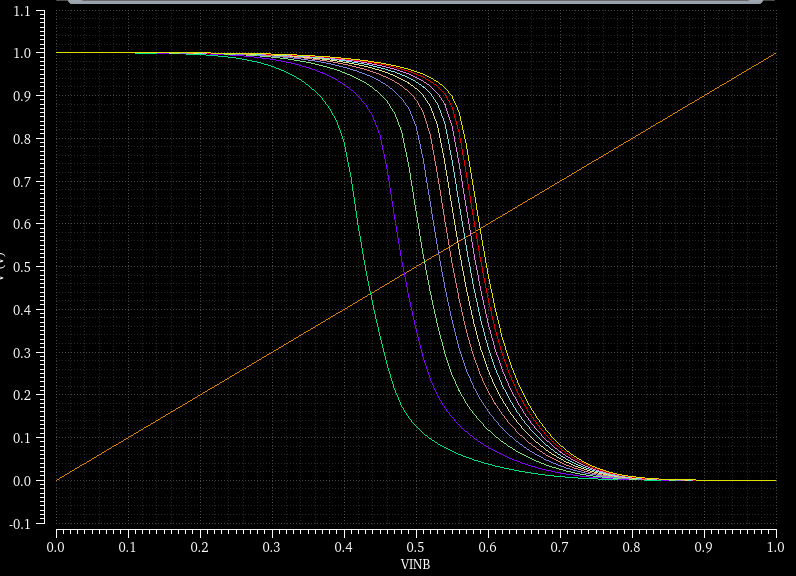

아래와 같은 그래프가 도출되는 것을 확인할 수 있다.

2u와 3u사이에 500m 값이 있는 것을 확인하였다. 정확한 값을 맞추기 위해 소수점 둘째 자리까지 범위를 넓혀 측정해 본다.

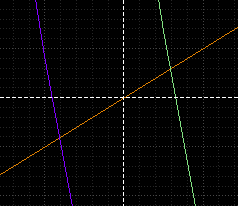

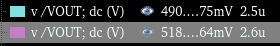

2.5u와 2.6u 사이에 0.5가 있는 것을 확인하였다. 둘째 자리까지 확대해 본다.

2.53u와 2.54u 사이에 500m 값이 존재하는 것을 확인했다.