Virtuoso : 2NAND GATE

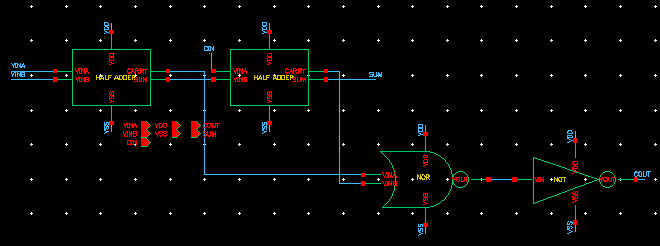

NOT Gate에 이어 이번에는 NAND Gate를 MobaXterm을 통해 구현해보려 한다. 먼저 개념정리를 하자면, AND일 경우에는 nMOS는 직렬, pMOS는 병렬이고OR일 경우에는 nMOS는 병렬, pMOS는 직렬로 구성된다. 만약 식이 F = (A * B + C)'인 경우에는 다음과 같이 회로가 그려진다. 그런데, 밑에 그림처럼도 그려질 수도 있다. 왼쪽 오른쪽 모두 다 동일한 구조지만, F선을 기준으로 맞닿는 TR의 개수가 다르기 때문에, 왼쪽의 회로도가 더 성능면으로 좋다고 판단할 수 있다. 즉, 딜레이 측면으로 성능이 유리하다.이번에는 F = (A*B + C*D)'의 회로를 그려보자. 다음과 같이 회로가 그려진다.2 NAND2 NAND를 설계하기 위해 다음과 같이 새로운 Cell V..